专注时间同步

专注时间同步装置 主营时间同步服务器设备

专注时间同步

专注时间同步装置 主营时间同步服务器设备

对于网络通信协议来说,主节点与从节点之间传输协议和数据包不会存在错误;但是对于硬件电路来说,就需要采用一定的方法来保证主从式时间同步。当主从时钟不一致时,就会导致通信信号丢失;同时,当主从式时间不同步时,也会导致主从节点之间出现传输数据包错误、网络拓扑错误。

1、原理介绍

在网络中,一个节点的时间信息通过时钟信号传递给另一个节点。一个时钟信号为1ns,如果另一个节点的时间信息为1ms,那么前者的时钟信号就是后者的2倍。如果后者的时钟信号也为10ms,那么两者之间就相差100ms。2、硬件实现

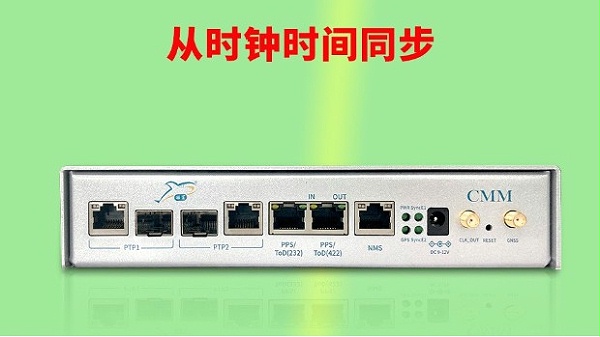

从时钟时间同步系统采用了FPGA设备方案。从时钟设备具有高精度、高性能、自主研发和高性价比等特点,能满足大多数用户对于时钟同步产品的要求。与此之外,设备内还集成了温度补偿、自研算法和时钟抖动补偿等技术,让从时钟时间同步精度更高。工业级芯片工作时首先通过外部时钟源产生一个时钟信号,接着再将该信号作为时钟同步信号发送到主从时钟芯片中。然后,主时钟从时钟还将内部集成了温度补偿和晶振驱动模块,在芯片内部的温度补偿电路和晶振驱动模块可以保证主从时钟芯片内部产生的时间信息是一致的;3、实物距离

CMM时钟同步产品,这是一个高精度从时钟,当CMM被用做从时钟时候,可以恢复主时钟时间至10ns精度。本身CMM设备采用12V供电,CMM从时钟产品配置OCXO晶振,具有人性化友好快速交互的WEB配置界面。总之如今从时钟时间同步是许多领域的重要技术,我们在时间领域主从齐发并进,让从时钟同步的精度更高。